Thông tin về STM8S103F3P6 có rất chi tiết và đầy đủ tại http://www.st.com/en/microcontrollers/stm8s103f3.html

Ngoài ra có thể tóm tắt các thông số chính sau:

- Core

- 16 MHz advanced STM8 core with Harvard architecture and 3-stage pipeline

- Extended instruction set

- Memories

- Program memory: 8 Kbyte Flash; data retention 20 years at 55 °C after 10 kcycle

- Data memory: 640 byte true data EEPROM; endurance 300 kcycle

- RAM: 1 Kbyte

- Clock, reset and supply management

- 2.95 to 5.5 V operating voltage

- Flexible clock control, 4 master clock sources

- Low power crystal resonator oscillator

- External clock input

- Internal, user-trimmable 16 MHz RC

- Internal low-power 128 kHz RC

- Clock security system with clock monitor

- Power management:

- Low-power modes (wait, active-halt, halt)

- Switch-off peripheral clocks individually

- Permanently active, low-consumption power-on and power-down reset

- Interrupt management

- Nested interrupt controller with 32 interrupts

- Up to 27 external interrupts on 6 vectors

- Timers

- Advanced control timer: 16-bit, 4 CAPCOM channels, 3 complementary outputs, dead-time insertion and flexible synchronization

- 16-bit general purpose timer, with 3 CAPCOM channels (IC, OC or PWM)

- 8-bit basic timer with 8-bit prescaler

- Auto wake-up timer

- Window watchdog and independent watchdog timers

- Communication interfaces

- UART with clock output for synchronous operation, SmartCard, IrDA, LIN master mode

- SPI interface up to 8 Mbit/s

- I2C interface up to 400 kbit/s

- Analog to digital converter (ADC)

- 10-bit, ±1 LSB ADC with up to 5 multiplexed channels, scan mode and analog watchdog

- I/Os

- Up to 28 I/Os on a 32-pin package including 21 high sink outputs

- Highly robust I/O design, immune against current injection

- Unique ID

- 96-bit unique key for each device

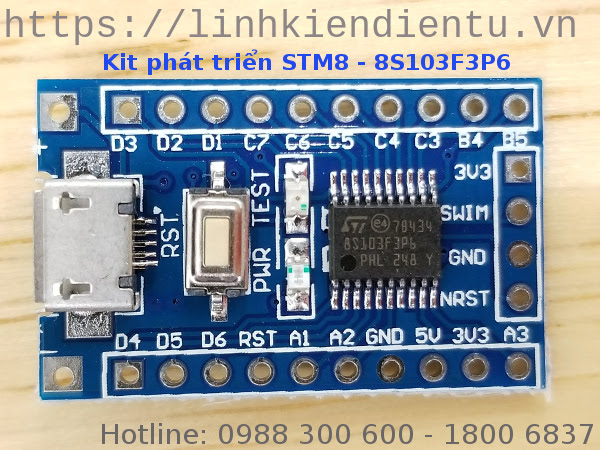

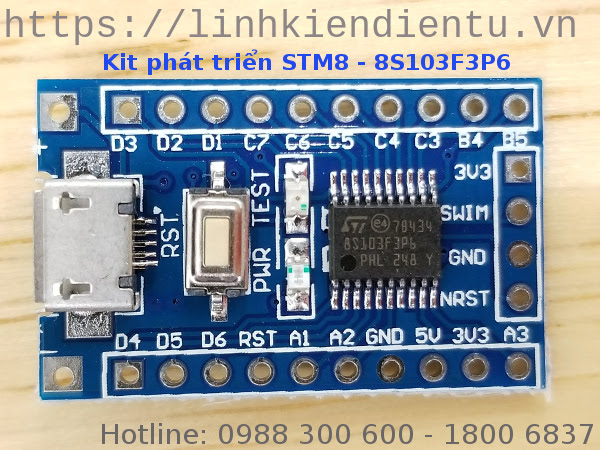

Hình ảnh ngõ ra của board